ADIVAnet

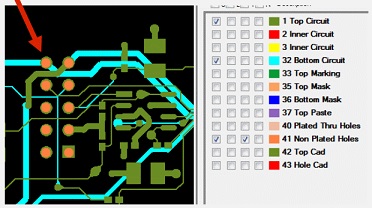

Find and report in a graphical manner net connectivity errors before product release. With ADIVA's Virtual Netlist Checking tool, designers can simulate the manufacturing netlist test process of a finished board during the design process. This verifies electrical integrity of design data before it is released to fabrication.